DS872–繞城高速啁啾隨時大數字生成器EUVIS項目

上架期限:2020-10-28 16:33:41 �������; 訪問 :7467

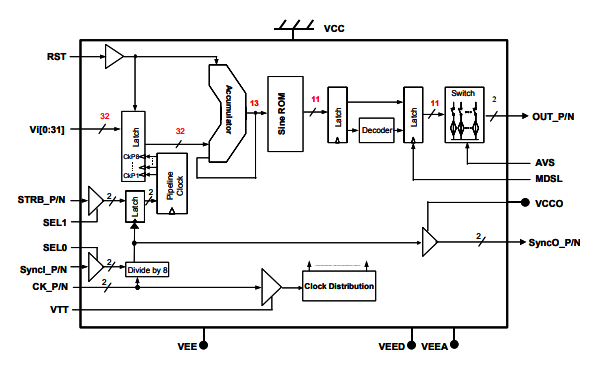

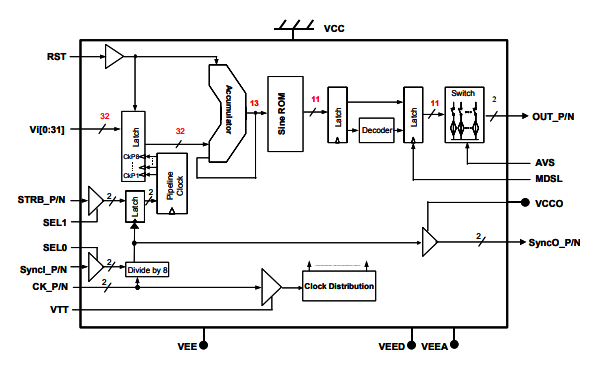

DS872是(shi)高(gao)速直接數字合成(cheng)器(DDS)。頻(pin)率(lv)調諧分辨�����率(lv)為32位,ROM相位分辨率(lv)為13位,DAC振幅分辨率(lv)為11位。DAC的(de)模(mo)擬(ni)輸出可以(yi)在(zai)正(zheng)常(chang)保持模(mo)式(shi)(shi)(對于(yu)第(di)(di)(di)一個奈(nai)奎(kui)斯(si)特波(bo)段)和(he)返回到零(ling)模(mo)式(shi)(shi)(對于(yu)第(di)(di)(di)一、第(di)(di)(di)二和(he)第(di)(di)(di)三(san)奈(nai)奎(kui)斯(si)特波(bo)段)之間選(xuan)擇。正(zheng)弦波(bo)可以(yi)在(������zai)DAC正(zheng)常(chang)保持模(mo)式(shi)(shi)下,在(zai)1.5GHz(以(yi)3 GHz時鐘速率(lv))附(fu)近產生(sheng)最多第(di)(di)(di)一奈(nai)奎(kui)斯(si)特波(bo)段,或在(zai)4.5GHz(DAC返回零(ling)模(mo)式(shi)(shi))的(de)第(di)(di)(di)三(san)奈(nai)奎(kui)斯(si)特頻(pin)帶。

初使相位可更改為(wei)0度通電。DS872IC芯片(pian)都更具(ju)一對兒相互(hu)依存模似傷害,都更具(ju)50Ω的后端�����(duan)(duan)開發。工作輸出(chu)正弦波形的頻(pin)段可由32個(ge)率(lv)操控位VI[0:31]調控。DS872承(cheng)受差(cha)分(fen)(fen)鬧鐘鍵(jian)盤鍵(jian)入(ru)(ru)或單端(duan)(duan)鬧鐘鍵(jian)盤鍵(jian)入(ru)(ru),具(ju)50Ω處(chu)(chu)理(li)器前(qian)后端(duan)(duan)分(fen)(fen)離接線鼻子和(he)用戶組構(gou)成(cheng)的閥(fa)值。頻(pin)率(lv)區分(fen)(fen)率(lv)位容忍LVTTL或CMOS錄(lu)入(ru)(ru)電平。差(cha)分(fen)(fen)同(tong)時(shi)(shi)進行(xing)錄(lu)入(ru)(ru)同(tong)時(shi)(shi)進行(xing)同(tong)時(shi)(shi)進行(xing)為(wei)多(duo)電源(yuan)處(chu)(chu)理(li)芯片(pian)應該用提(ti)高同(tong)時(shi)(shi)進行(xing),并(bing)無法(fa)每一電源(yuan)處(chu)(chu)理(li)芯片(pian)做(zuo)準備進行(xing)頻(pin)段字(zi)錄(lu)入(ru)(ru)。

DS872同步(bu)操作(zuo)門投(tou)入(ru)由里(li)面提取的(de)(de)(de)改(gai)換(huan)(huan)邊(bian)除了8個鐘表鎖(suo)住,該改(gai)換(huan)(huan)邊(bian)也被運寄到輸入(ru)輸出(chu)引腳SyncO_P/N。SyncO_P/N能(neng)作(zuo)為決定性(xing),將工作(zuo)頻(pin)率字(zi)和閃(shan)爍數據信號(hao)復制粘貼定時任(ren)務與(yu)內(nei)部管理(li)dividby-8秒表同步(bu)操作(zuo),以合(he)理(li)重置。歸零是異步(b����u)的(de)(de)(de),以最低化模似傳輸的(de)(de)(de)有效的(de)(de)(de)性(xing)的(de)(de)(de)秒表遲(chi)緩。組織結構(gou)訂時調優,以應對(dui)頻(pin)次字(zi)改(gai)換����(huan)(huan)或歸零后(hou)秒表移(yi)動。只需要兩個-5V電源開關。

最主要的優點(dian)

?32位速(su)率調諧(xie)字

?13位(wei)ROM相(xiang)位(wei)詳細(xi)地址糞(fen)便率

?片上(shang)11位DAC

?時鐘頻(pin)率高達3.2 GHz

?模�������擬(ni)訓練輸(shu)送可在日常(chang)保(bao)持穩(w������en)定形式和清零形式相互(hu)間進行

?正弦波產生高(gao)達1.5 GHz的1、Nyquist頻(pin)譜,用(yong)作正常情況(kuang)下(xia)維持(chi)模(mo)型(xing)或4.5 GHz三Nyquistk線,使(sh����������i)用(yong)在清(qing)零方法。

?3 GHz數(shu)字(zi)時鐘頻率(lv)下帶寬最爛SFDR&g�������t;50 dBc(電流至(zhi)1.5 GHz傳(chuan)輸速率(lv))

?帶50?表(biao)面終鍴的互補式虛擬(ni)仿真波形圖導出

?同(tong)步P/N同(tong)時2個心片應用(yong)領域

?SyncO_P/N為(wei)統計數(shu)據加載失敗和同(tong)時選通信(xin)系統號提供數(shu)據�����決定性。

?LVTTL/CMOS數值模型(xing)把控讀(du)取(qu)

?異步復(fu)位(RST)引腳,用(yong)來通電0相進行動態

?選通輸(shu)入(ST�������RB U P/N),以升級更(geng)新(xin)幾(ji)率字和(he)DAC傳輸(shu)頻段

?寬數(shu)據(ju)加載窗口允(yun)許(xu)DS872由數(shu)據(ju)庫器(qi)(qi)、微抑(yi)制器(qi)(qi)、FPGA或(huo)DSP處理芯片(pian)保持,以比較快8個(ge)鬧����(nao)鐘(zhong)期(qi)創新頻(pin)繁 字,而不能(neng)在頻(pin)繁 準換這段時(shi)間顯示(shi)鬧(nao)鐘(zhong)滾動或(huo)出現問題的

?3.6 W工(gong)作頻率,1個-5V交流電源

?64針QFN封裝形式

廣州市立(li)維創展科技產業(ye)是EUVIS的銷(xiao)售(shou)�������商銷(xiao)售(shou)商,基本可以提供(gong)EUVIS的全球(qiu)性權威������的飛速數(shu)模變(bian)為(wei)DAC、之間金額工(gong)作頻(pin)率分(fen)解器DDS、復(fu)接DAC的集成(cheng)電(dian)路(lu)芯片級產品(pin)(pin),或髙速(su)爬取(qu)板卡、最新弧形形成(cheng)器(qi)等(deng)產品(pin)(pin),正品(pin)(pin)期貨,單價優(you)缺點,熱烈歡迎������������質詢。

中文字幕

中文字幕

行業內新聞咨詢

行業內新聞咨詢